MaskPlace: Fast Chip Placement via Reinforced Visual Representation Learning

A new chip placement method based on visual representation learning.

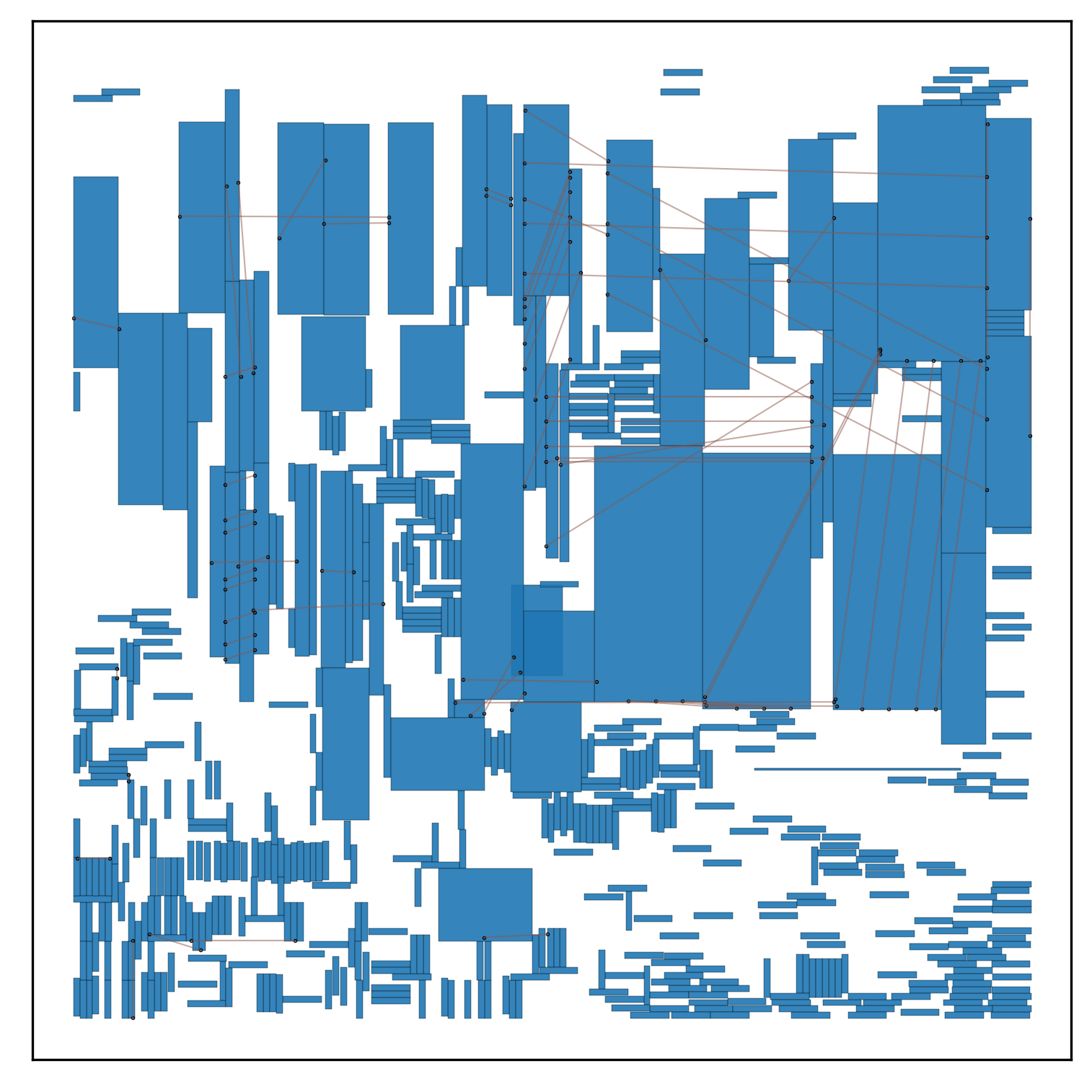

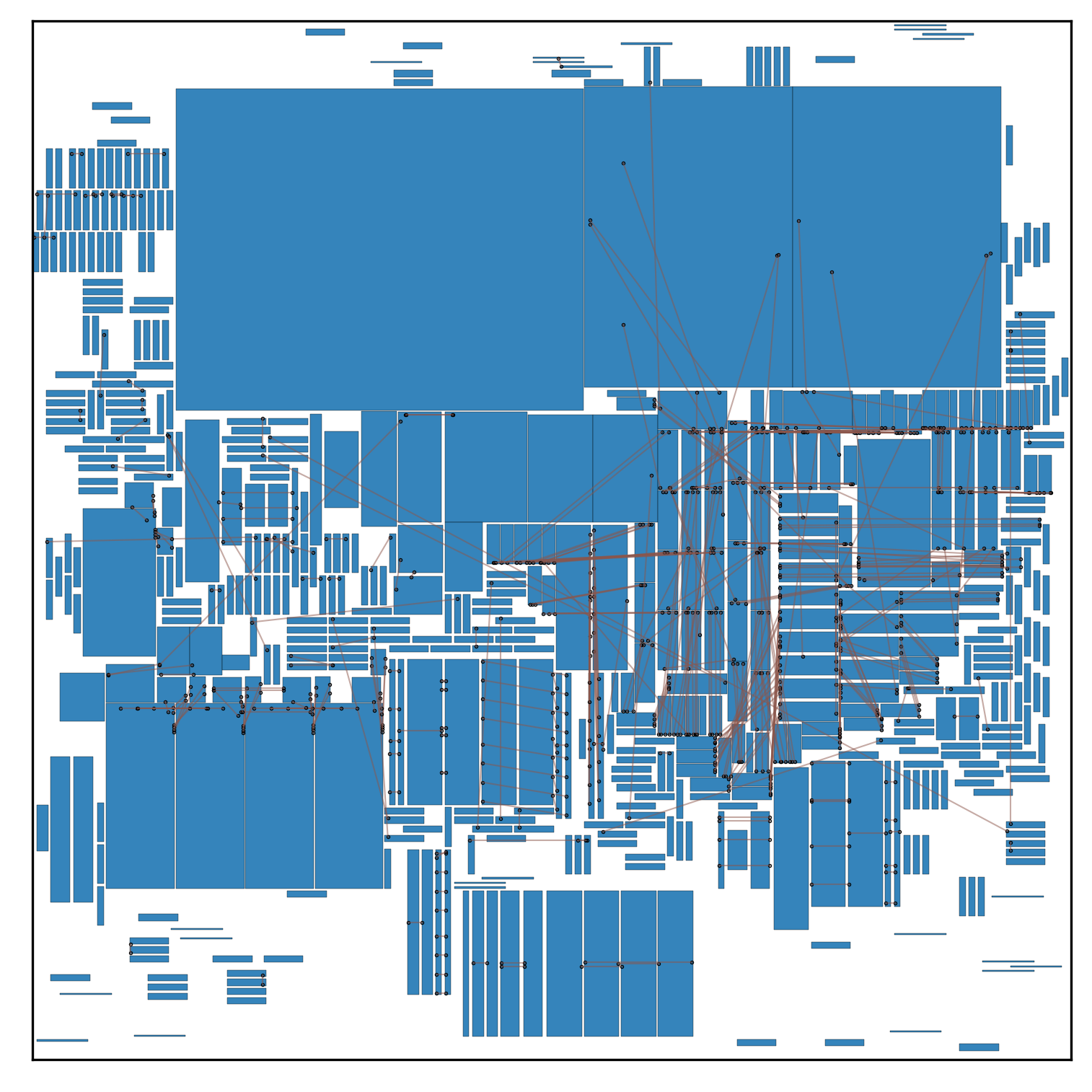

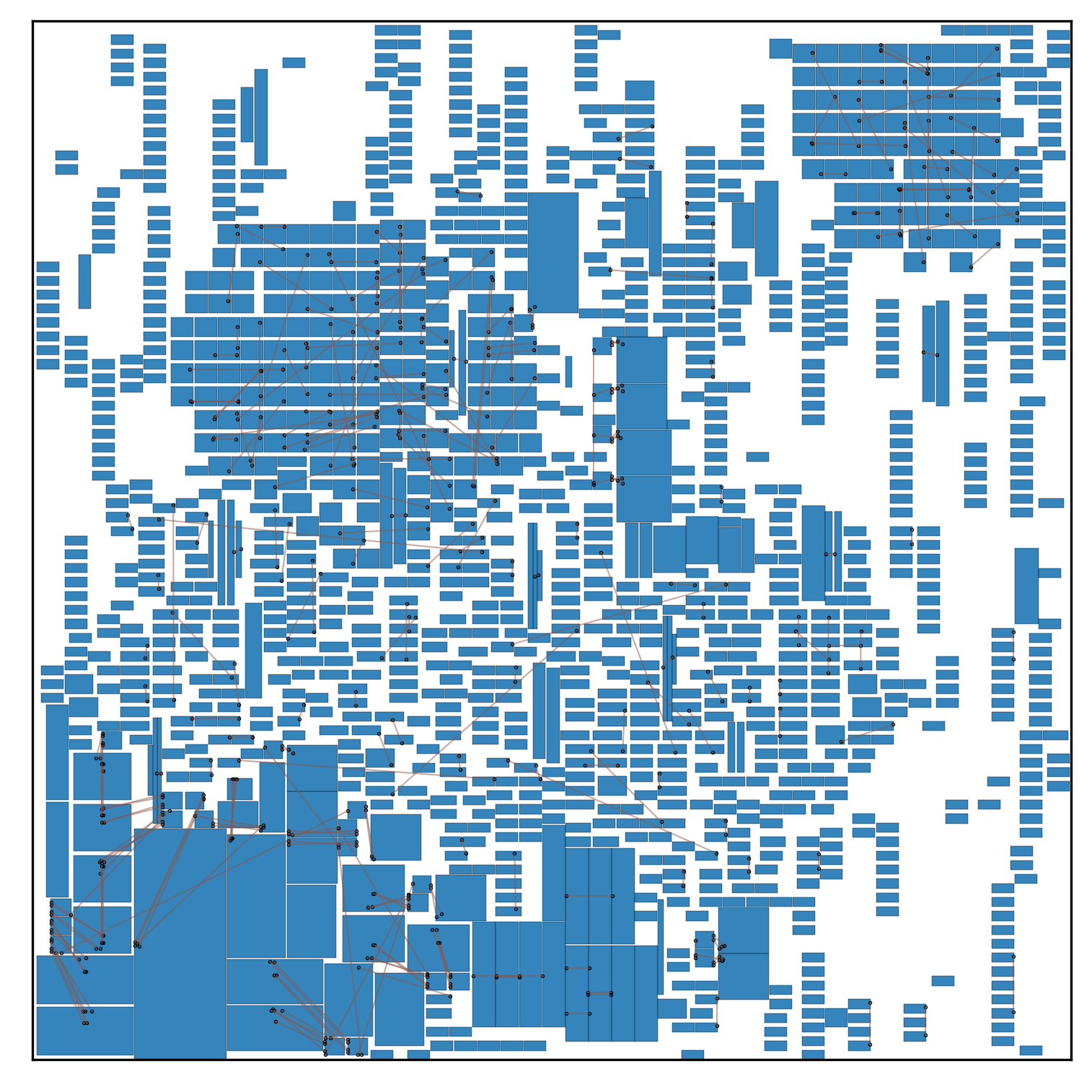

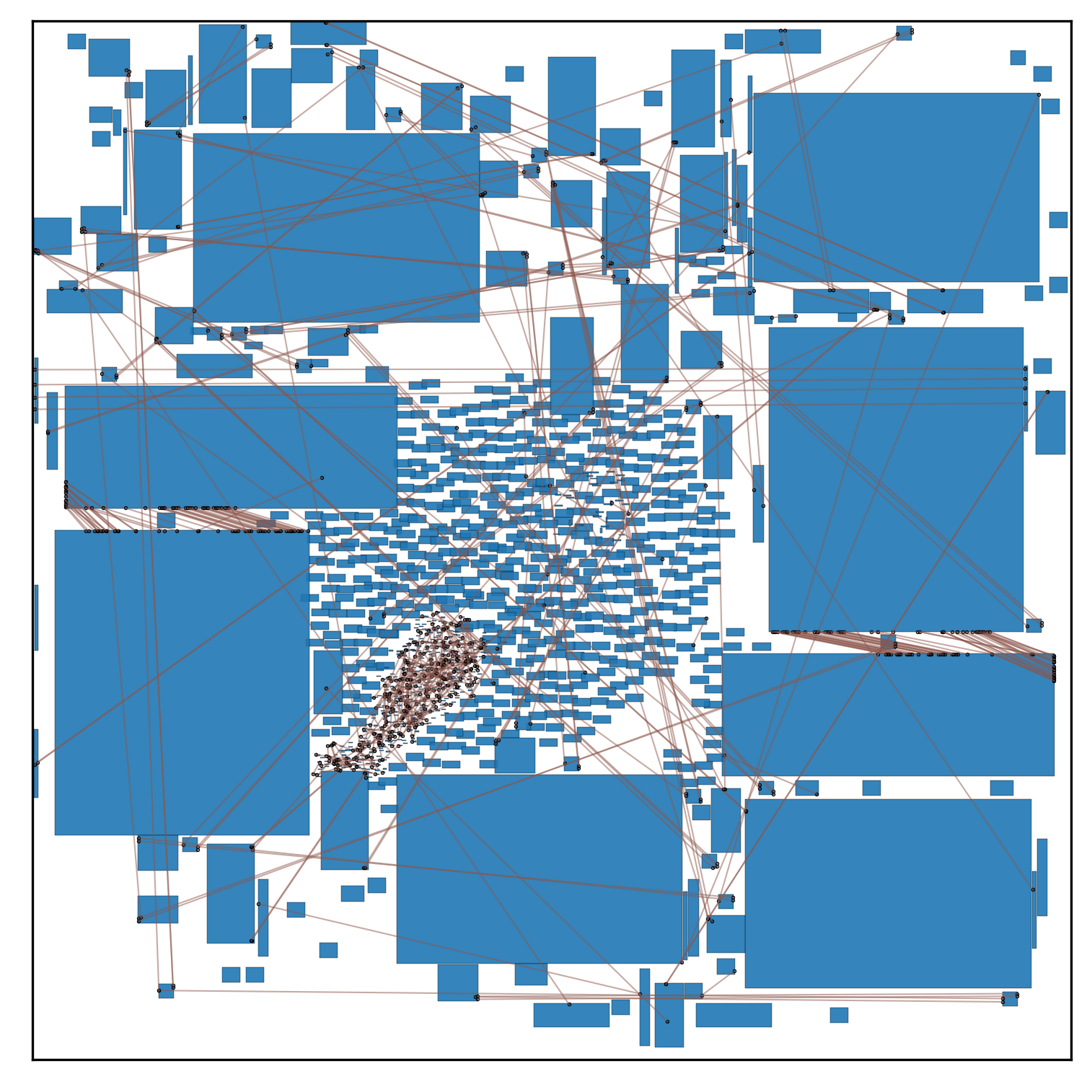

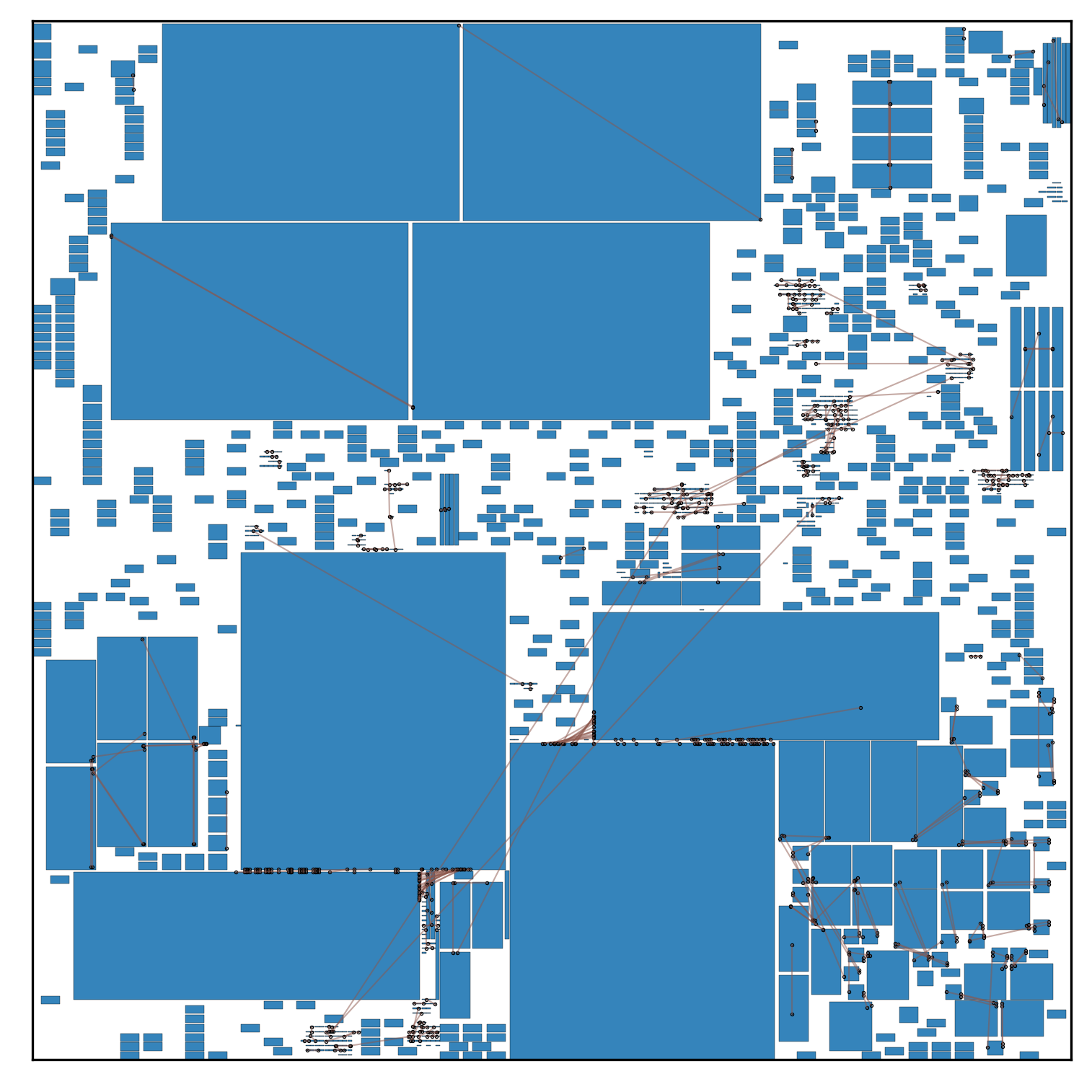

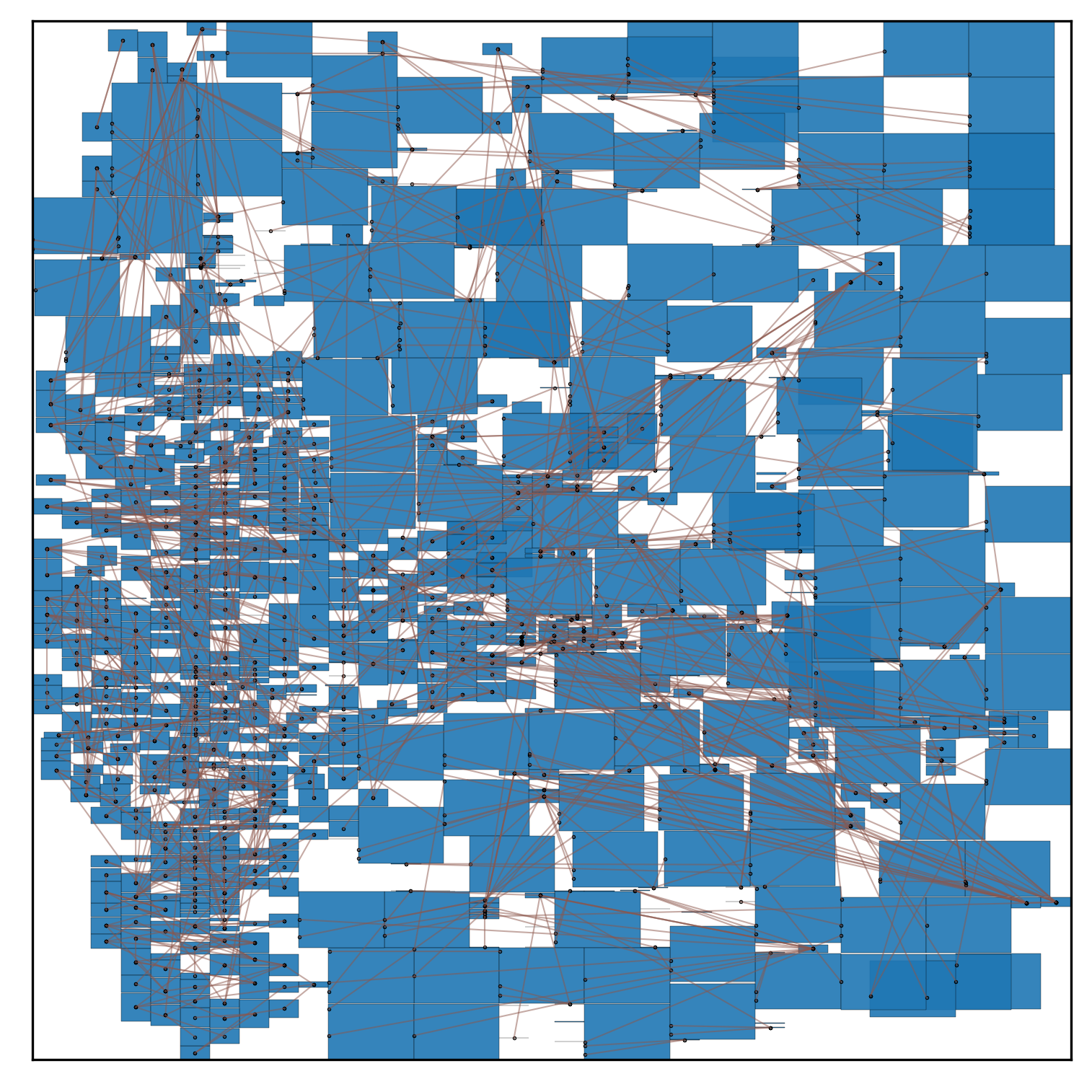

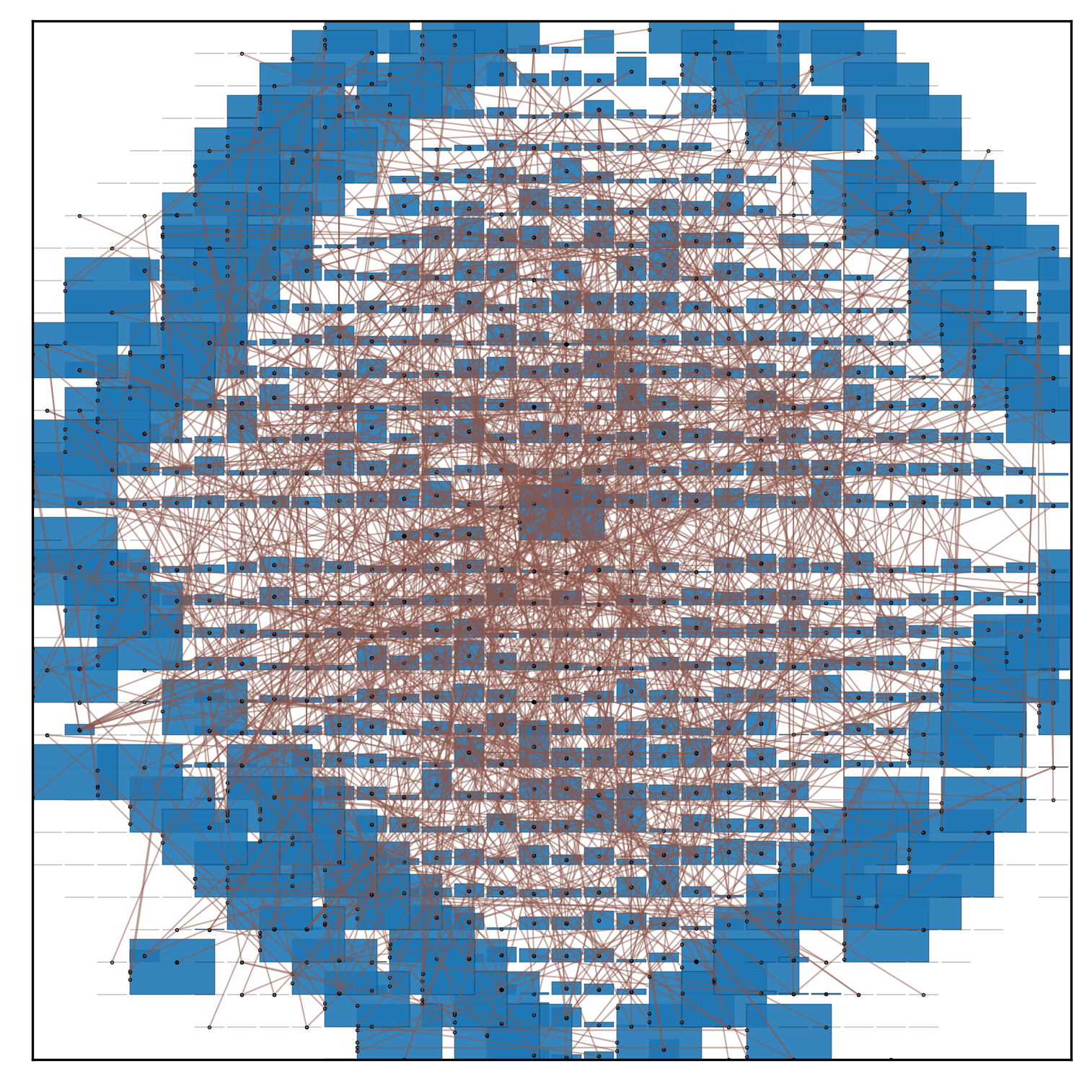

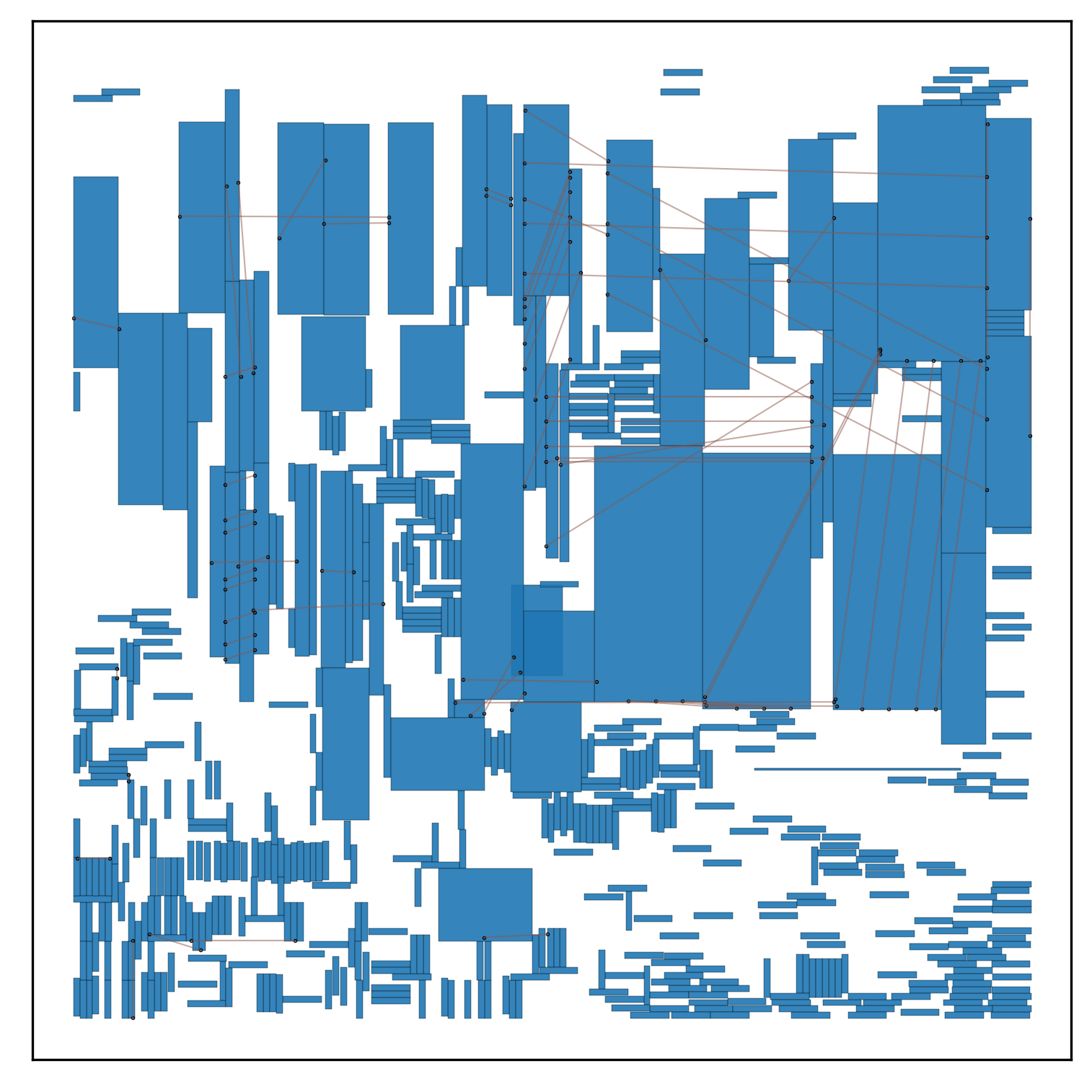

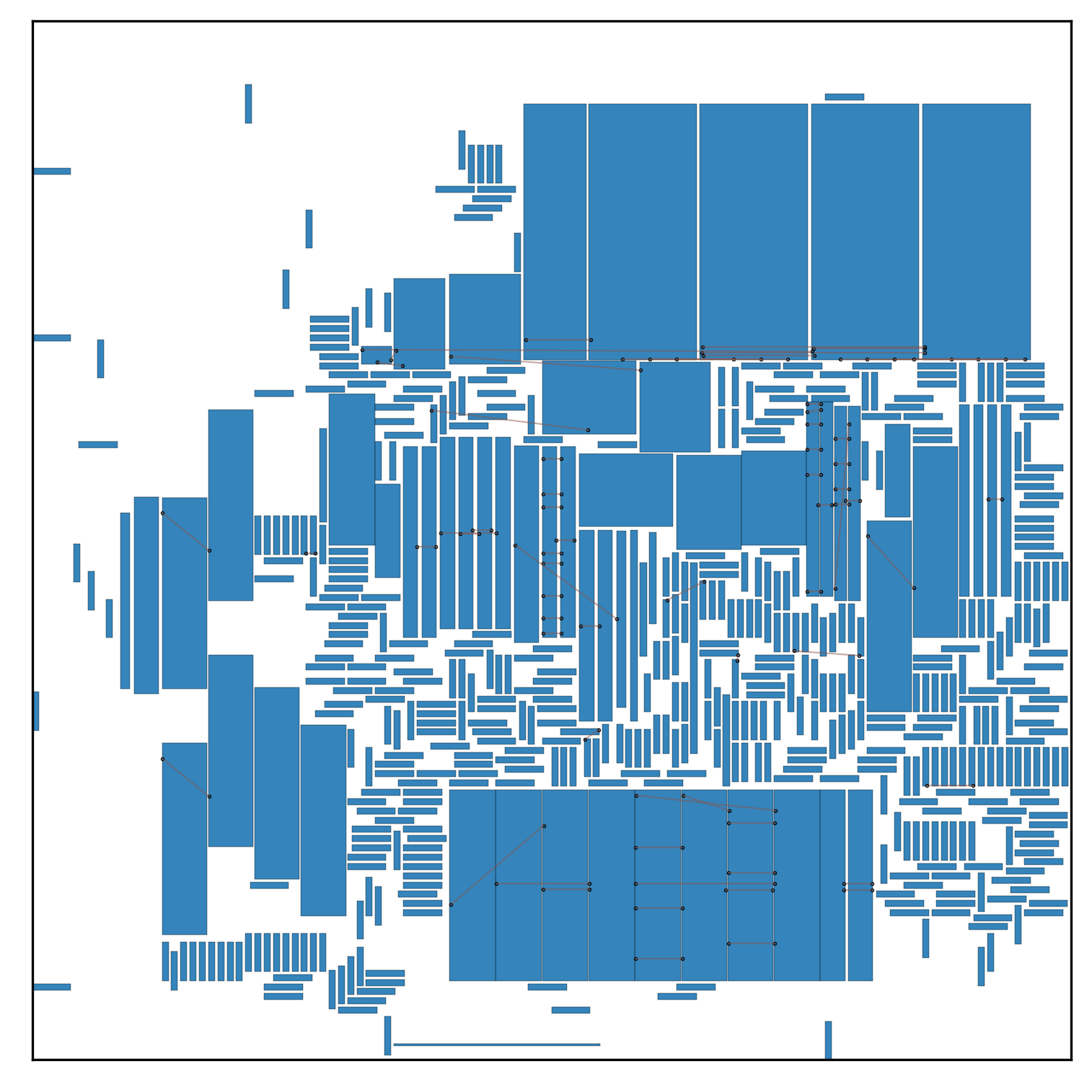

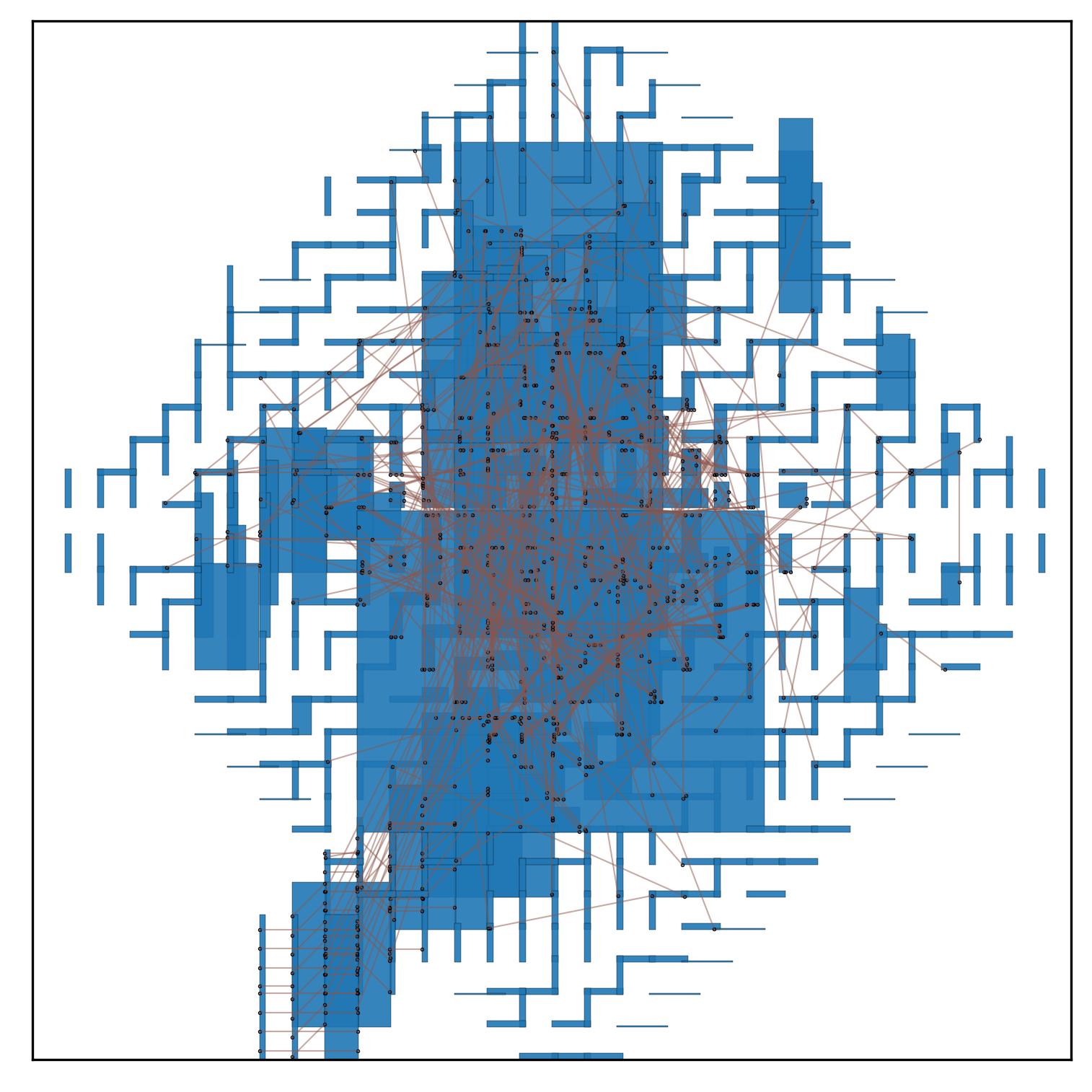

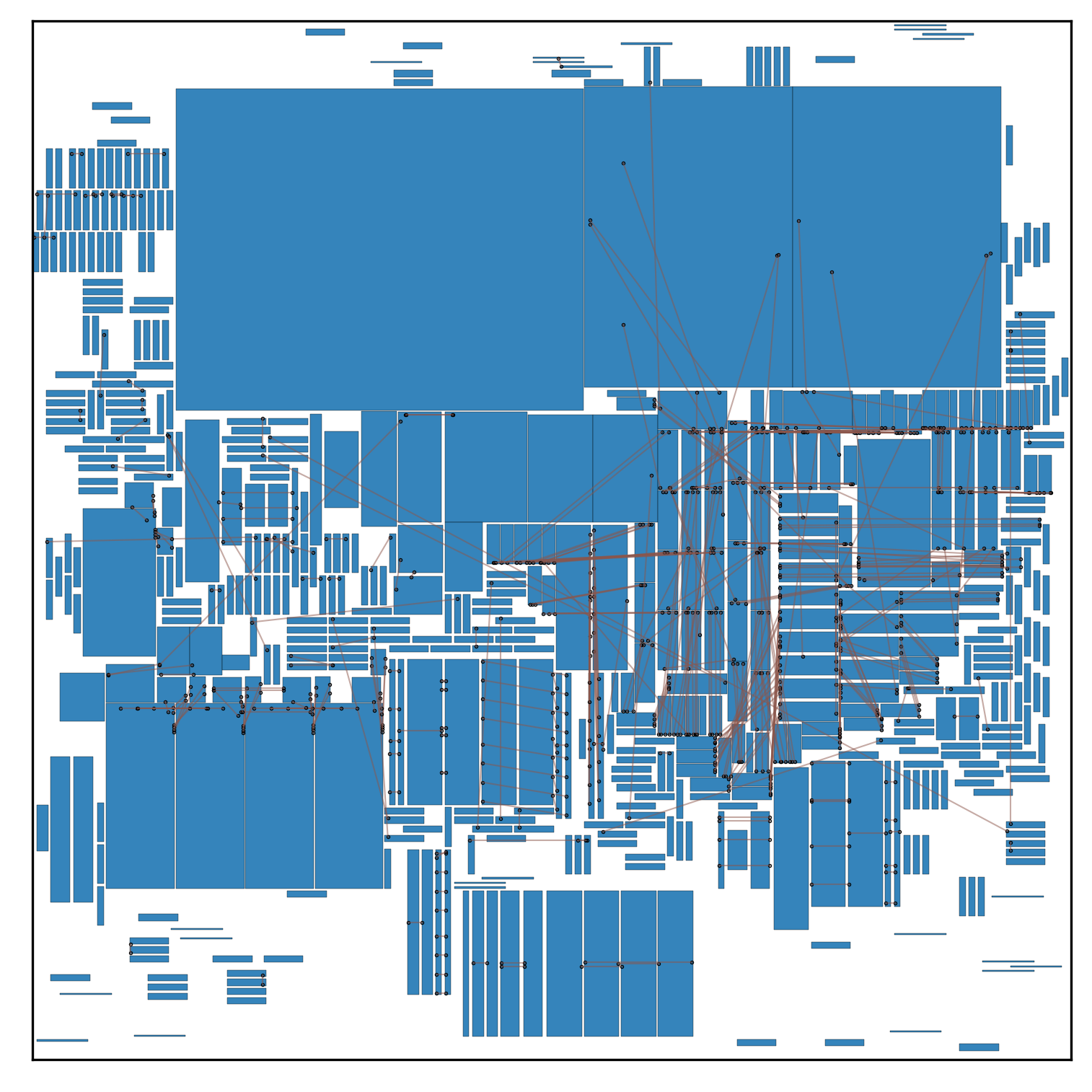

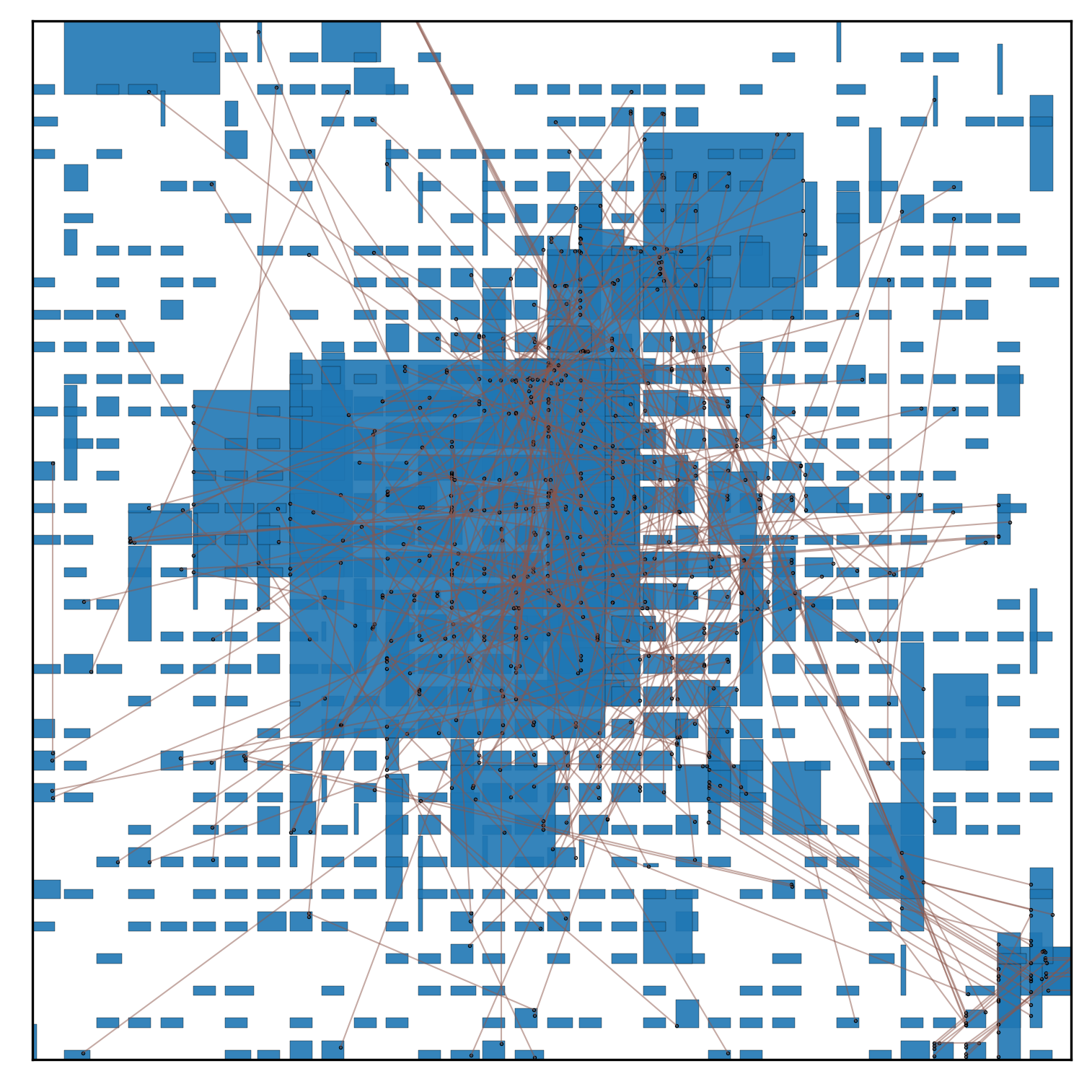

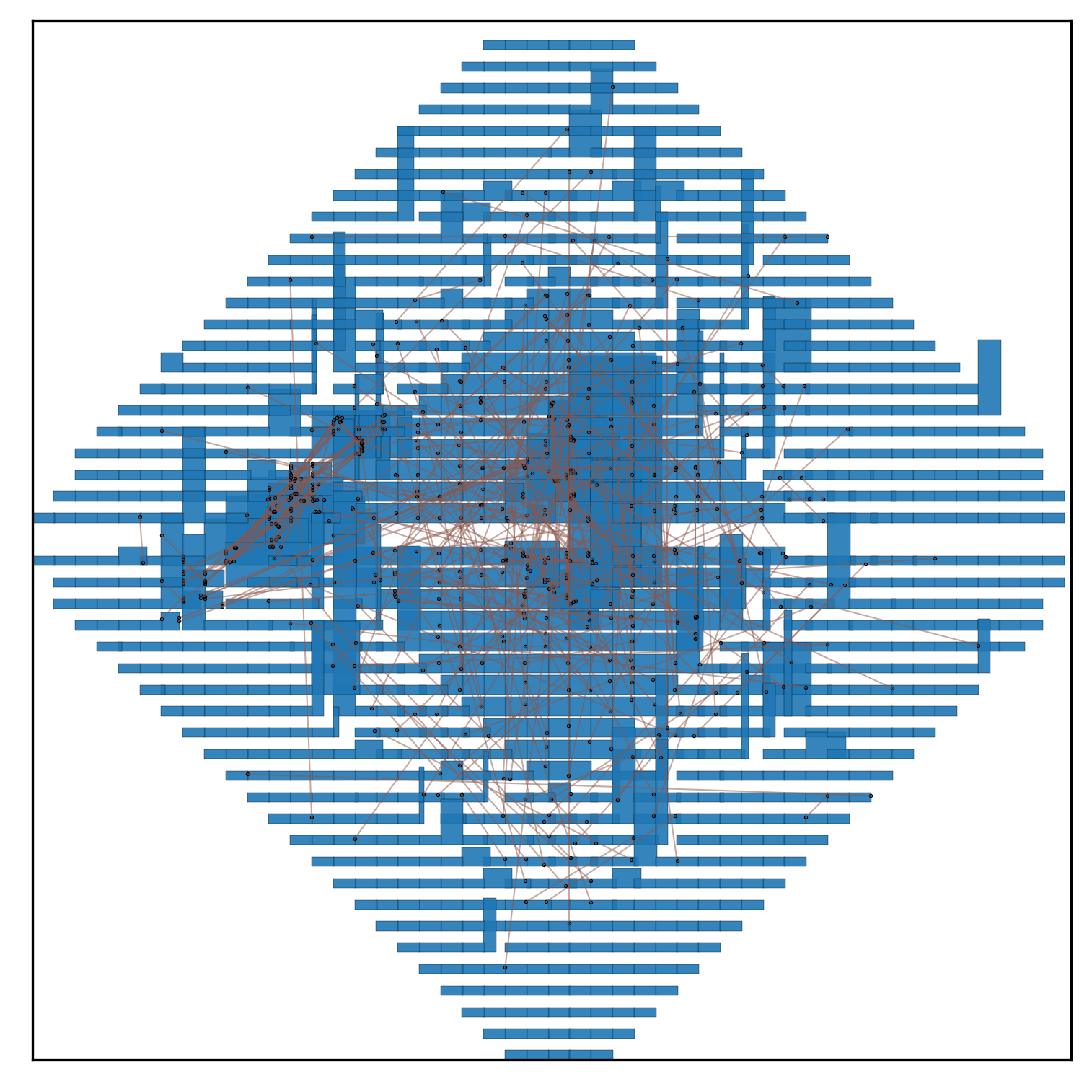

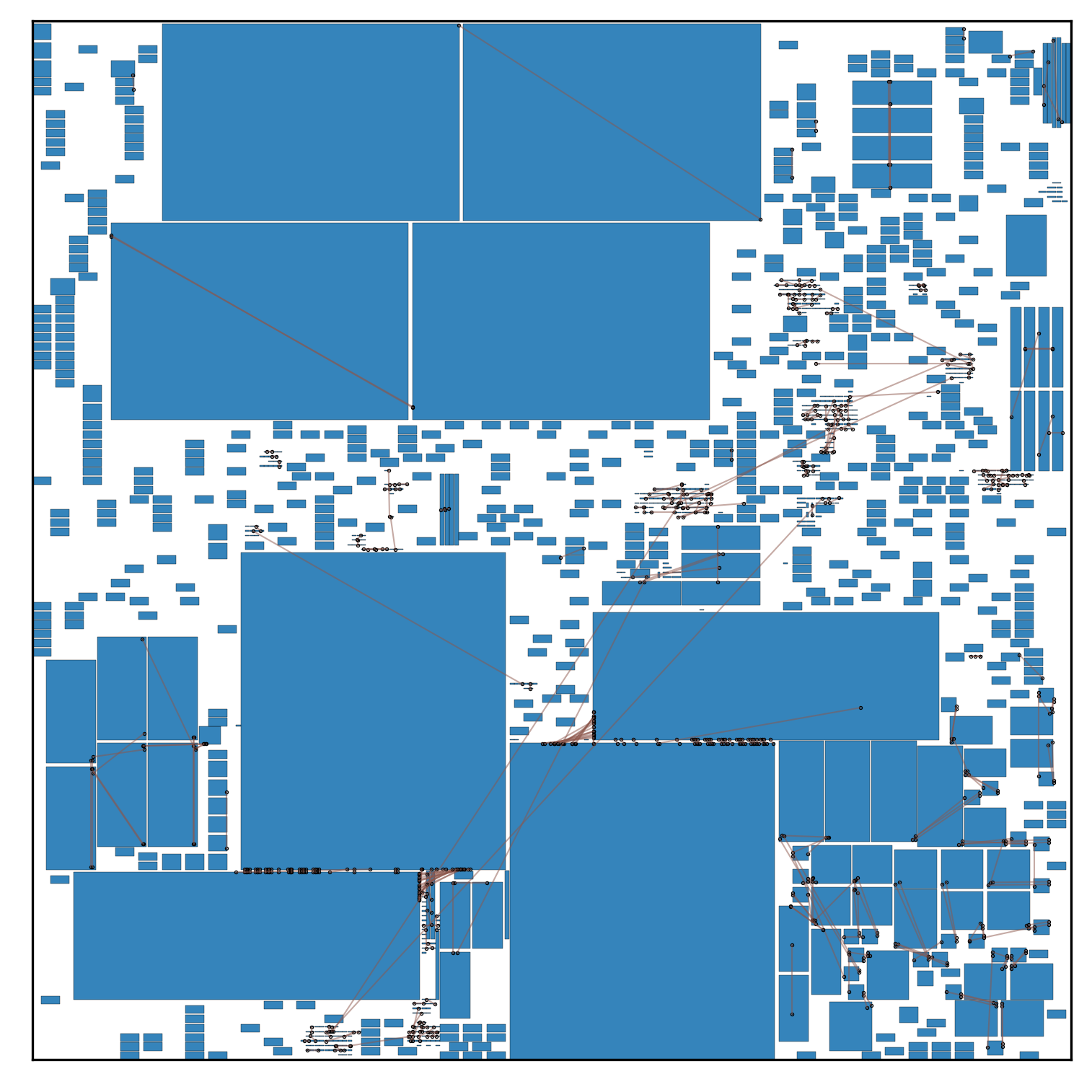

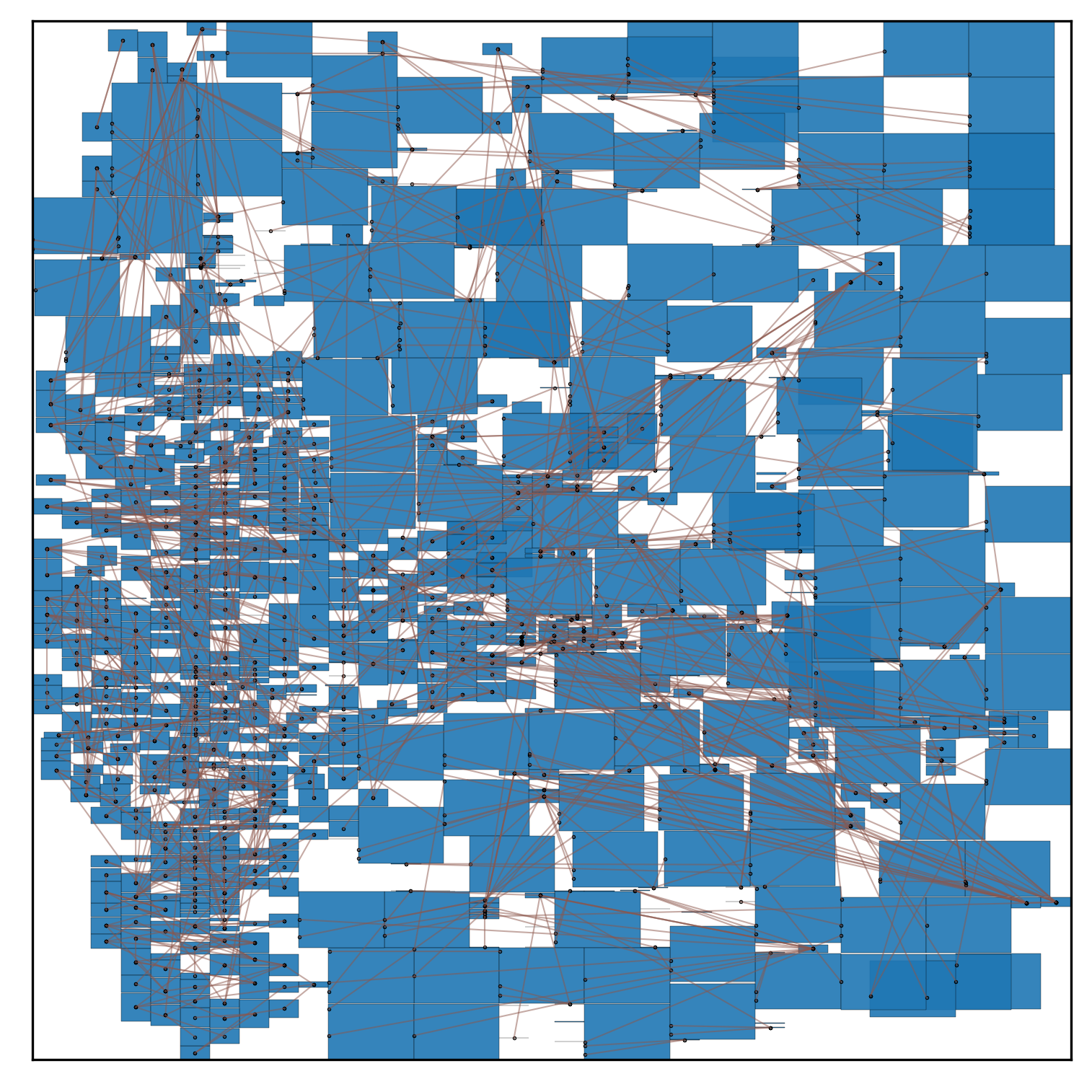

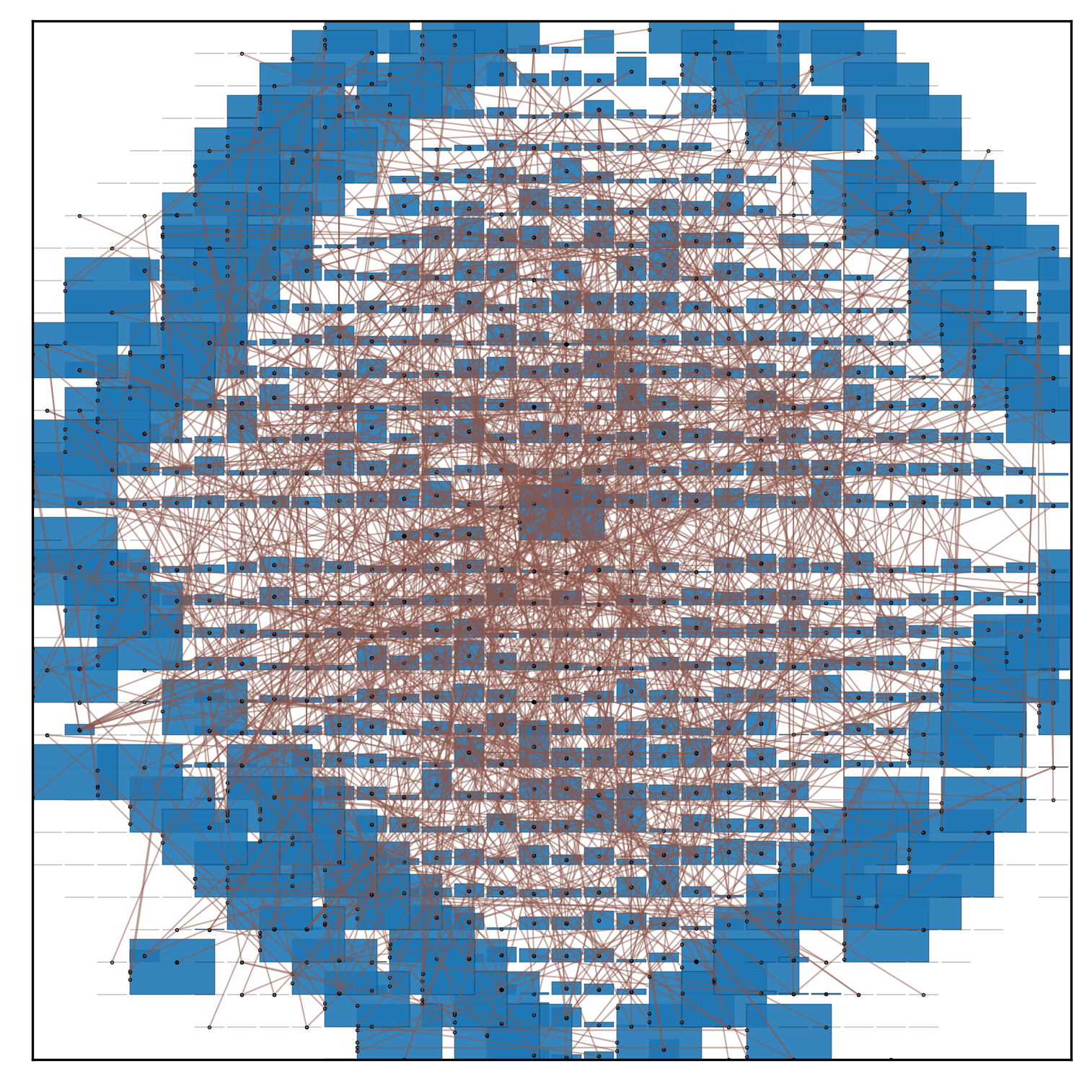

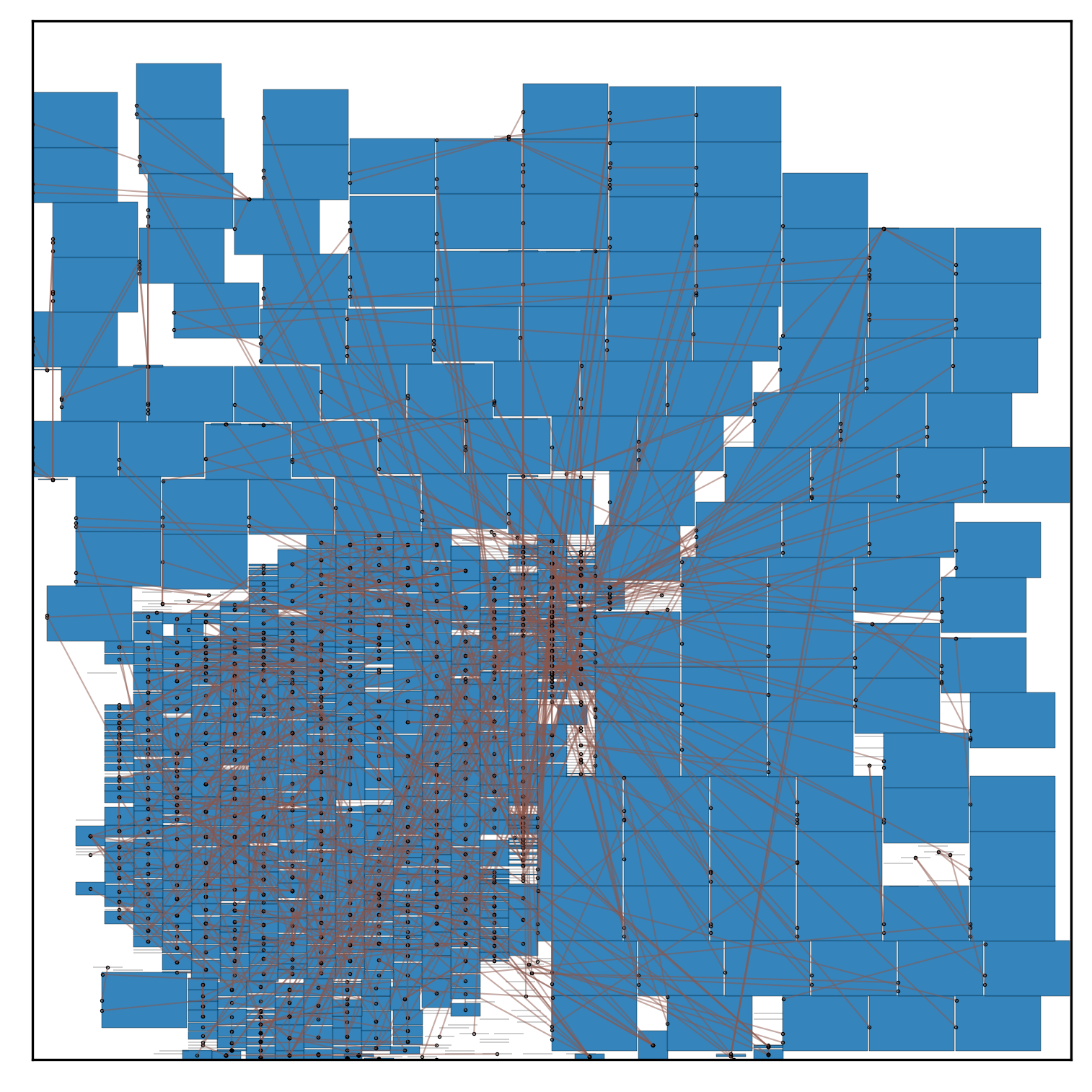

The placement process animation

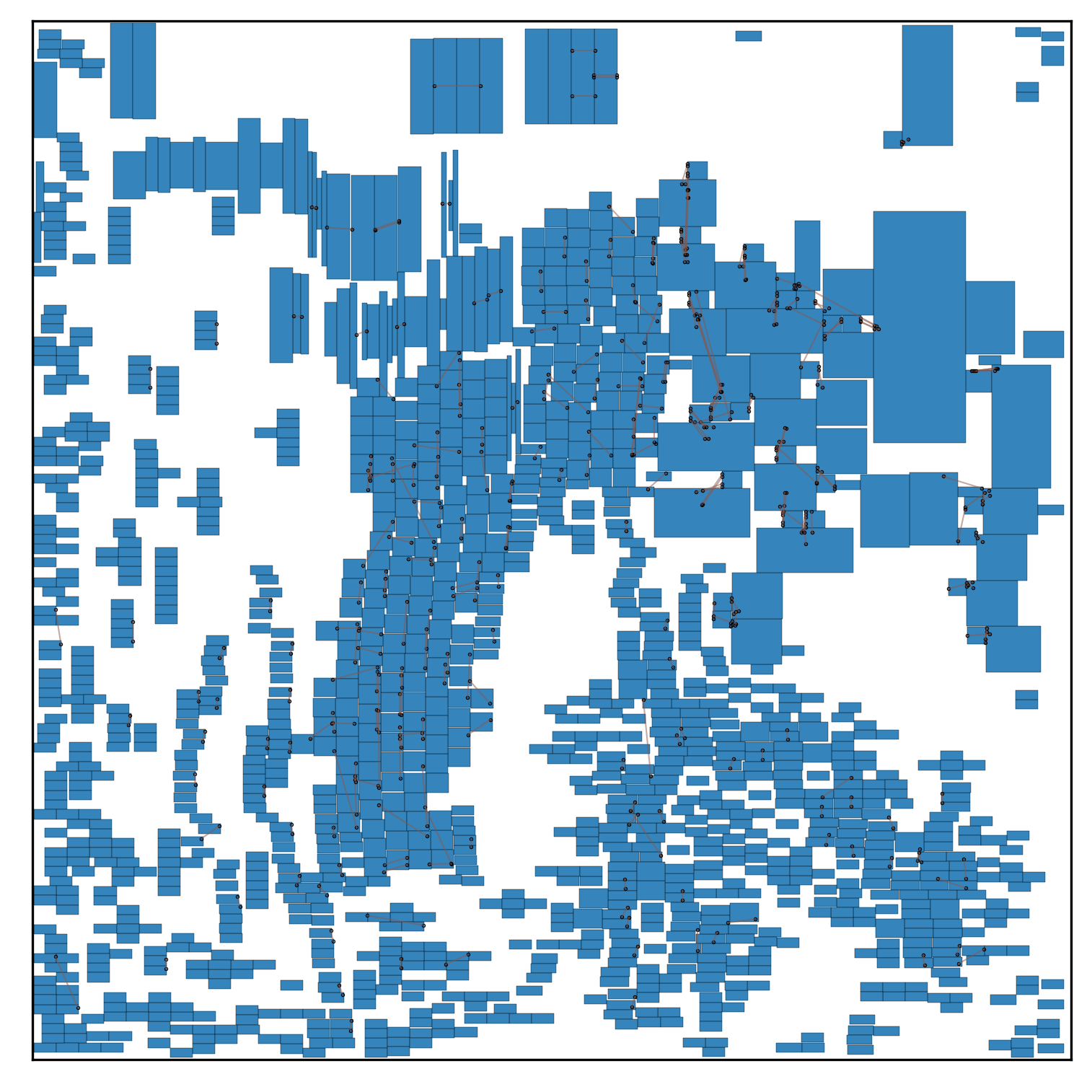

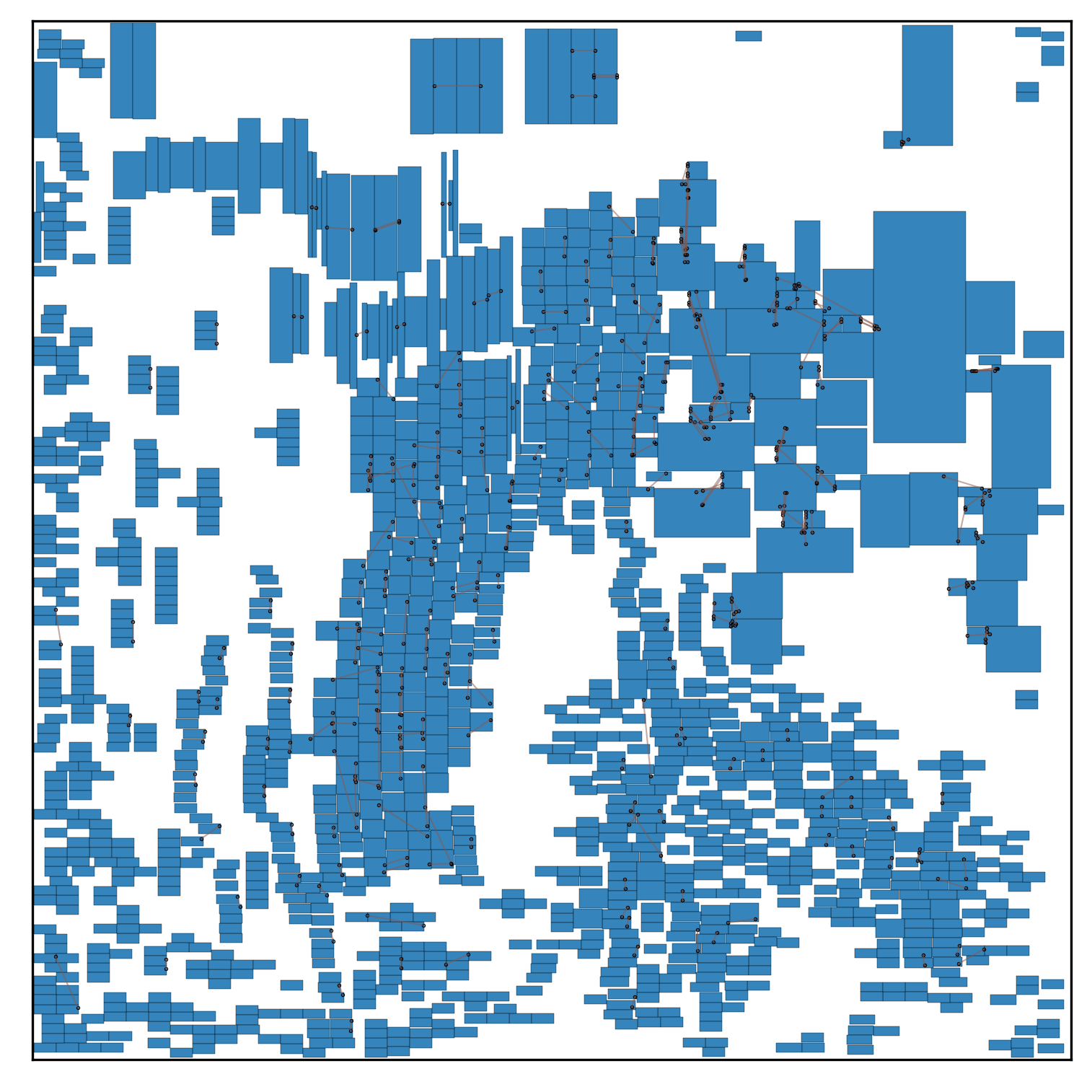

Benchmark: Bigblue3

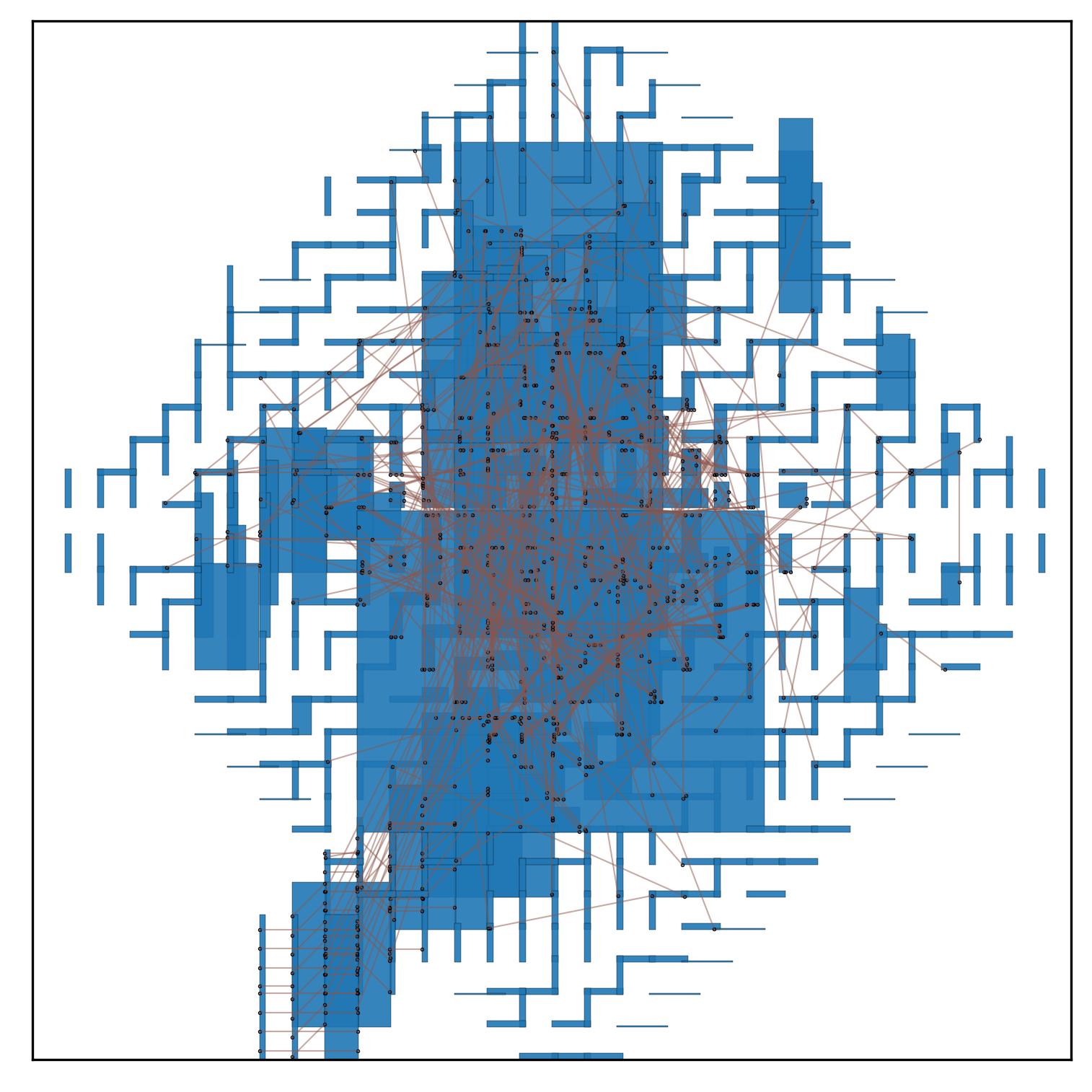

| Placement |

Pos Mask t |

Wire Mask t |

|

|

|

| View Mask |

Pos Mask t+1 |

Wire Mask t+1 |

|

|

|

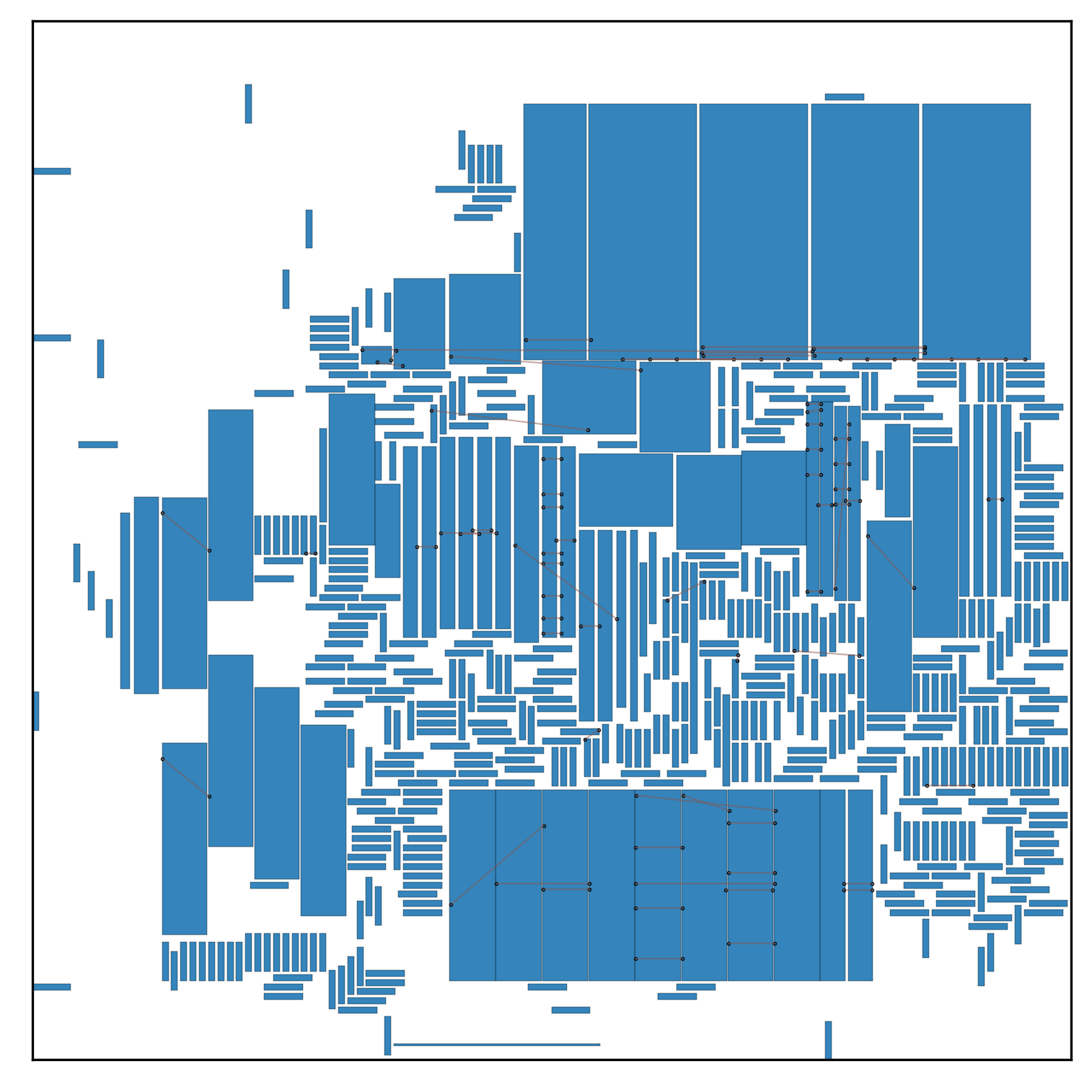

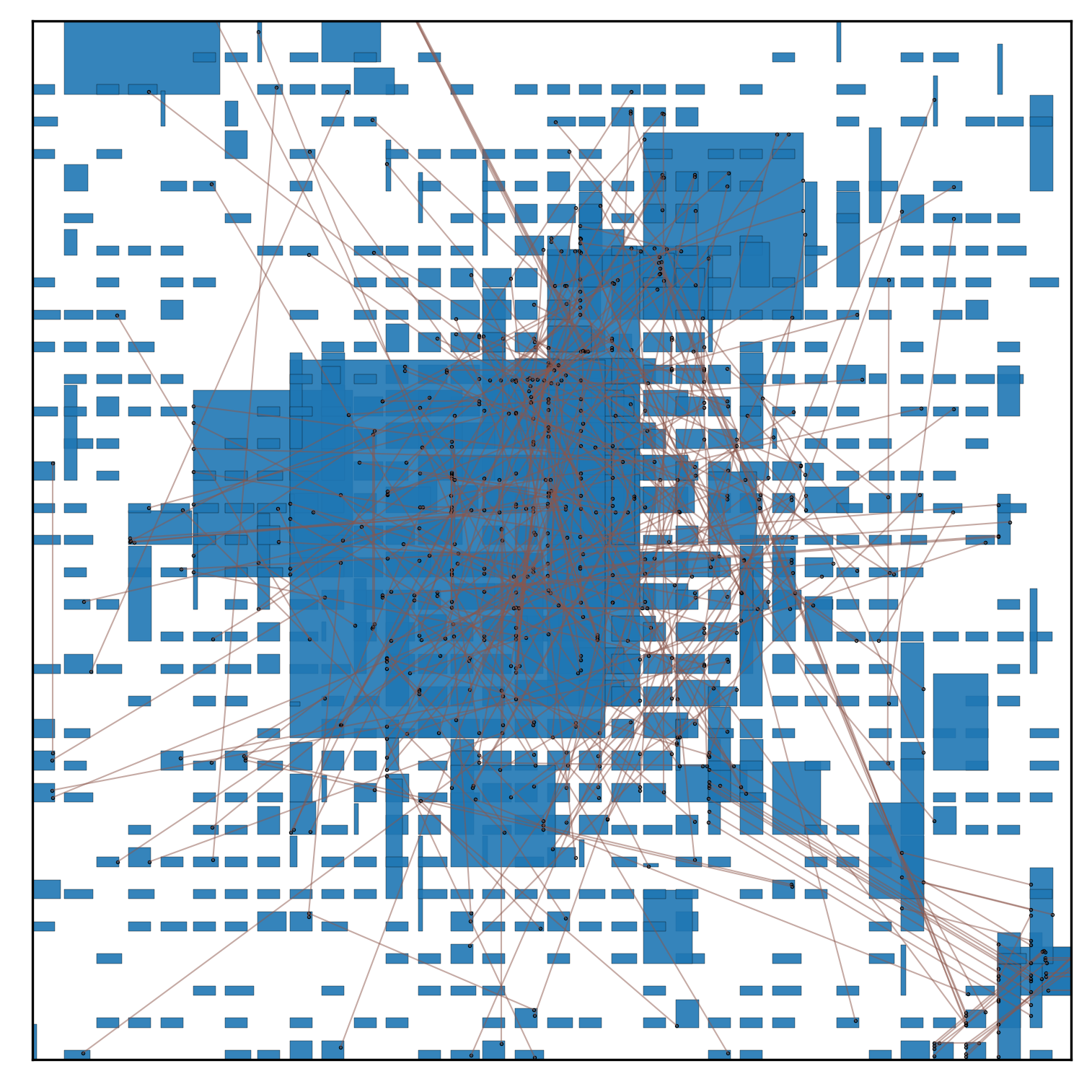

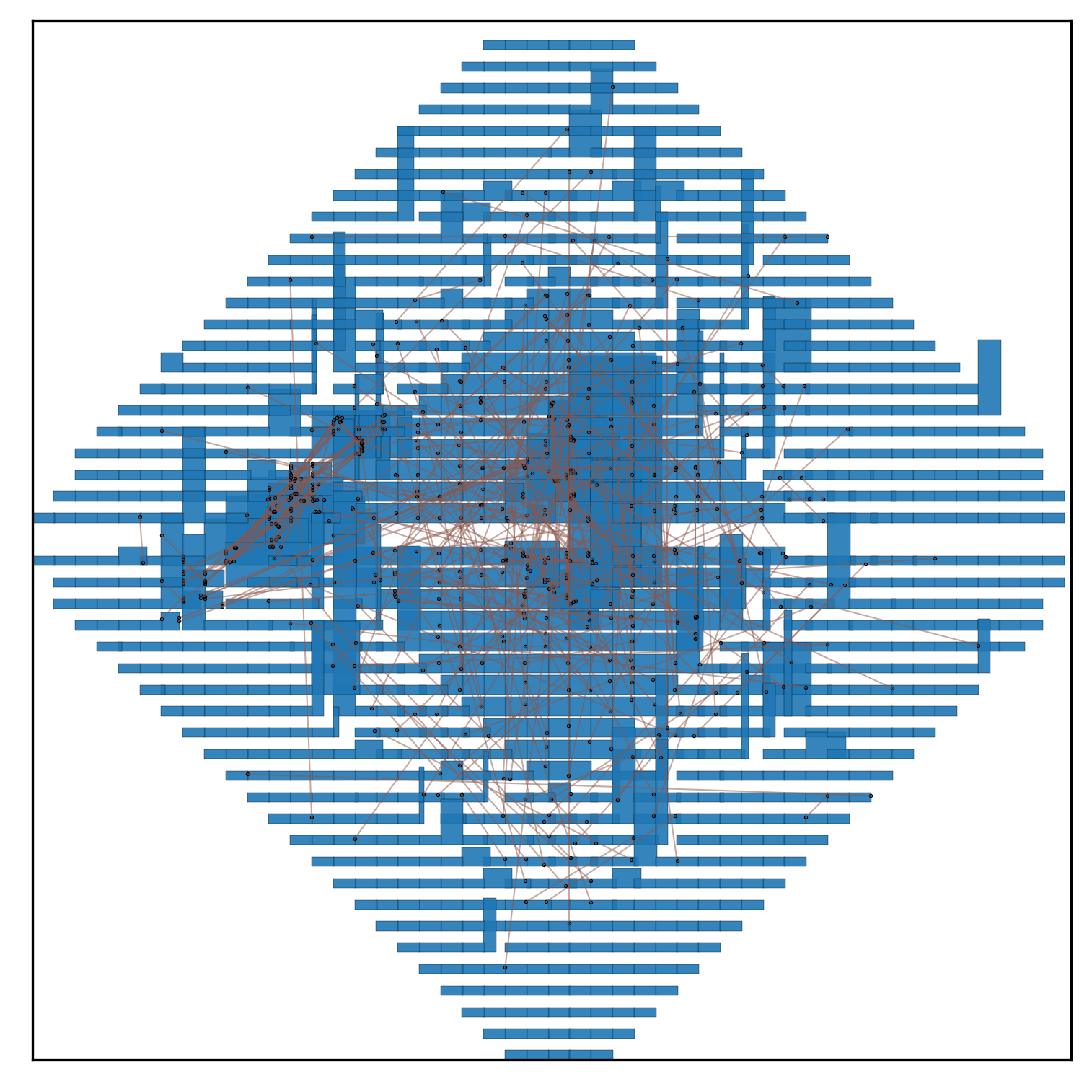

Standard Cell Placement

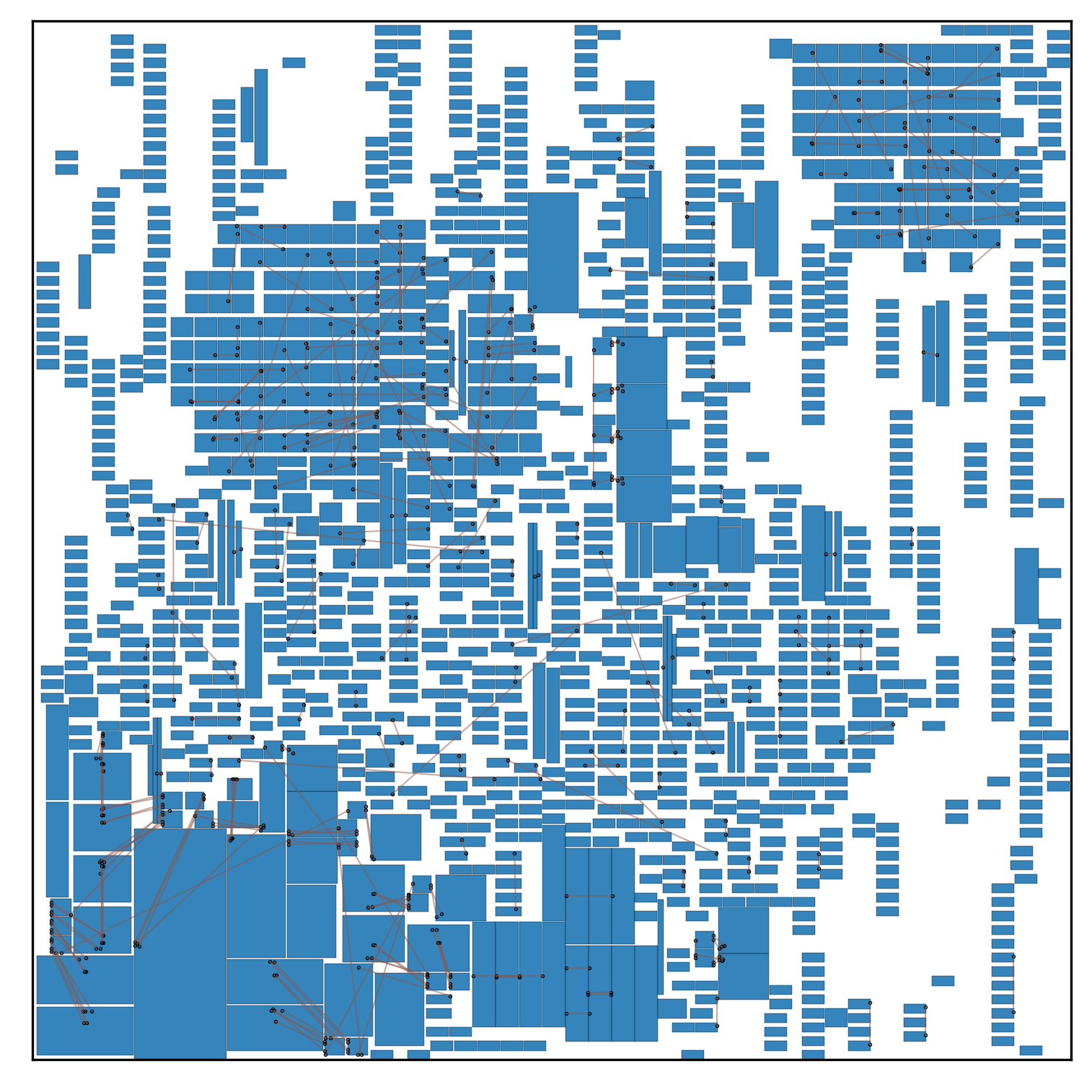

| adaptec2 |

adaptec4 |

bigblue3 |

|

|

|

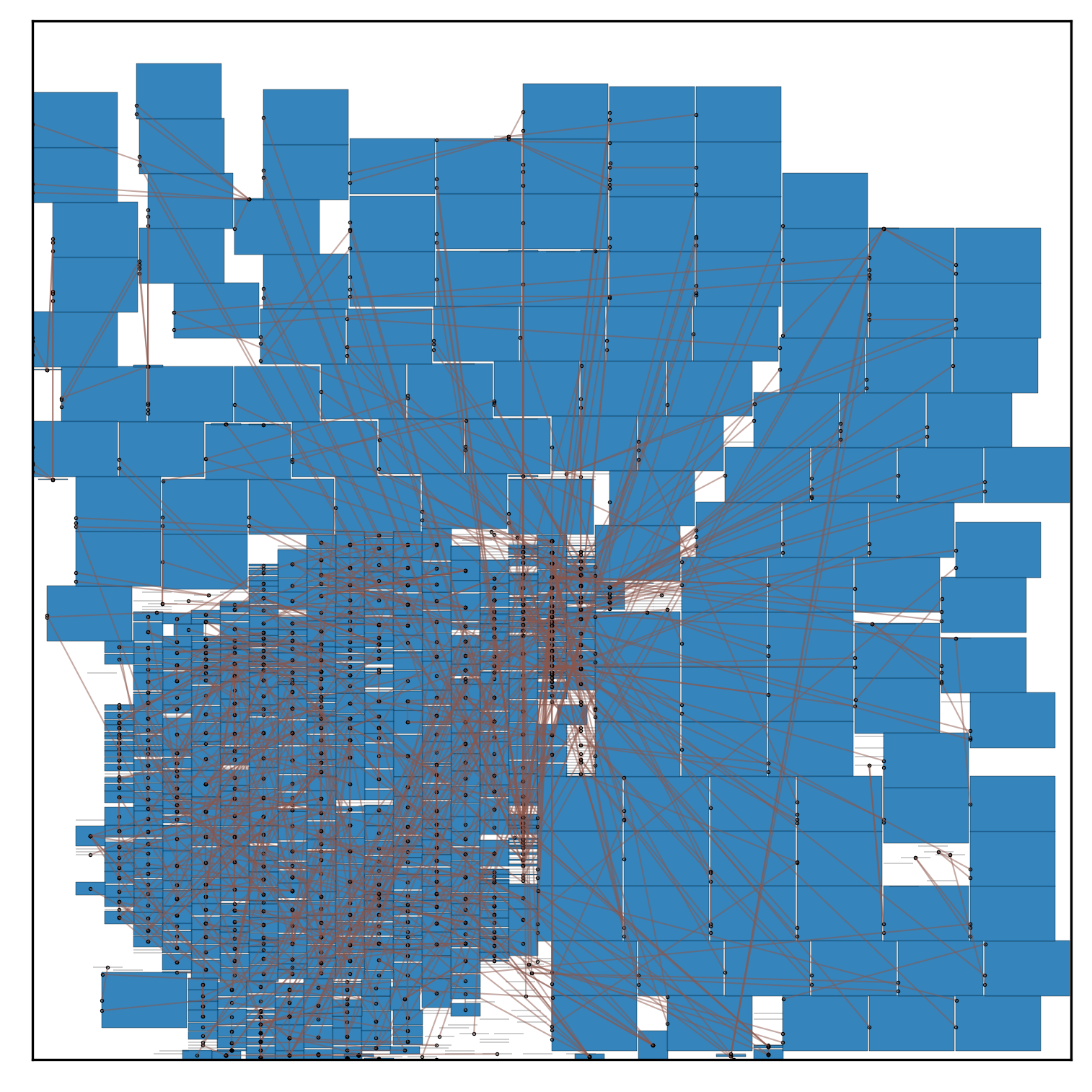

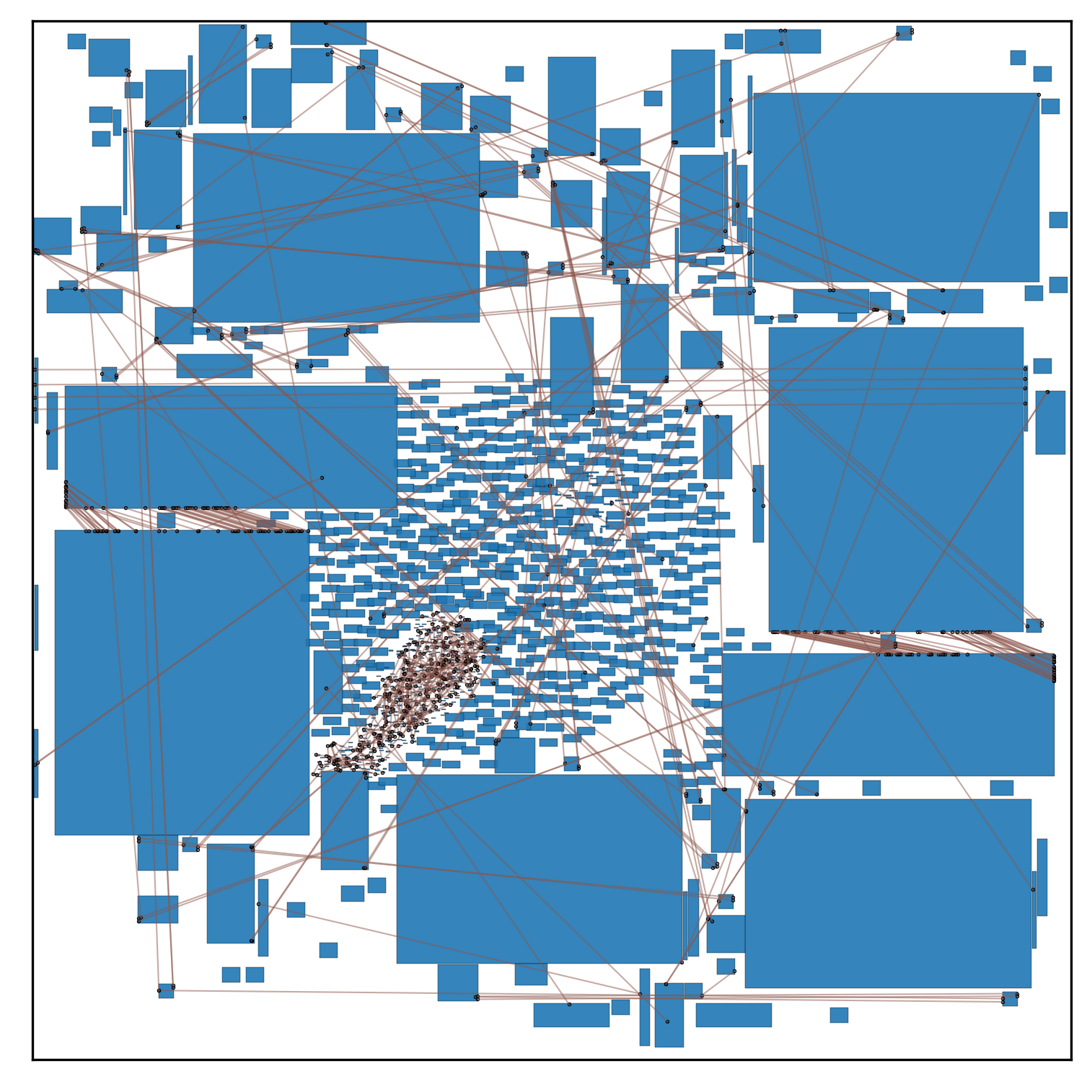

Full Benchmark demonstration

| Benchmark |

DREAMPlace |

Graph |

DeepPR |

MaskPlace |

| adaptec1 |

|

|

|

|

| HPWL (105) |

17.94 |

26.05 |

21.36 |

6.57 |

| Wirel (105) |

19.24 |

28.54 |

25.64 |

7.36 |

| adaptec2 |

|

|

|

|

| HPWL (105) |

135.32 |

359.35 |

197.13 |

79.98 |

| Wirel (105) |

140.91 |

381.64 |

205.78 |

83.59 |

| adaptec3 |

|

|

|

|

| HPWL (105) |

112.28 |

392.66 |

340.29 |

79.33 |

| Wirel (105) |

119.23 |

409.37 |

372.02 |

85.28 |

| adaptec4 |

|

|

|

|

| HPWL (105) |

37.77 |

152.89 |

243.12 |

75.75 |

| Wirel (105) |

47.90 |

179.43 |

290.14 |

88.87 |

| bigblue1 |

|

|

|

|

| HPWL (105) |

2.50 |

8.32 |

20.49 |

2.42 |

| Wirel (105) |

3.41 |

10.00 |

25.68 |

3.14 |

| bigblue3 |

|

|

|

|

| HPWL (105) |

104.05 |

345.49 |

439.09 |

82.61 |

| Wirel (105) |

107.58 |

373.33 |

517.86 |

88.51 |

| ariane |

|

|

|

|

| HPWL (105) |

20.30 |

16.83 |

51.43 |

14.86 |

| Wirel (105) |

21.72 |

18.48 |

55.85 |

15.80 |